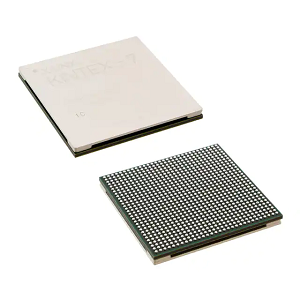

XC7K420T-2FFG901I - Mizunguko Iliyounganishwa, Iliyopachikwa, Safu za Lango Zinazoweza Kupangwa kwenye Sehemu

Sifa za Bidhaa

| AINA | MFANO |

| kategoria | Mizunguko Iliyounganishwa (ICs)Imepachikwa Safu za Lango Zinazoweza Kupangwa (FPGAs) |

| mtengenezaji | AMD |

| mfululizo | Kintex®-7 |

| kanga | trei |

| Hali ya bidhaa | Inayotumika |

| DigiKey inaweza kupangwa | Haijathibitishwa |

| Nambari ya LAB/CLB | 32575 |

| Idadi ya vipengele/vitengo vya mantiki | 416960 |

| Jumla ya idadi ya biti za RAM | 30781440 |

| Idadi ya I/Os | 380 |

| Voltage - Ugavi wa nguvu | 0.97V ~ 1.03V |

| Aina ya ufungaji | Aina ya wambiso wa uso |

| Joto la uendeshaji | -40°C ~ 100°C (TJ) |

| Kifurushi/Makazi | 900-BBGA,FCBGA |

| Ufungaji wa sehemu ya muuzaji | 901-FCBGA (31x31) |

| Nambari kuu ya bidhaa | XC7K420 |

| AINA | MFANO |

| kategoria | Mizunguko Iliyounganishwa (ICs)Imepachikwa |

| mtengenezaji | AMD |

| mfululizo | Kintex®-7 |

| kanga | trei |

| Hali ya bidhaa | Inayotumika |

| DigiKey inaweza kupangwa | Haijathibitishwa |

| Nambari ya LAB/CLB | 32575 |

| Idadi ya vipengele/vitengo vya mantiki | 416960 |

| Jumla ya idadi ya biti za RAM | 30781440 |

| Idadi ya I/Os | 380 |

| Voltage - Ugavi wa nguvu | 0.97V ~ 1.03V |

| Aina ya ufungaji | Aina ya wambiso wa uso |

| Joto la uendeshaji | -40°C ~ 100°C (TJ) |

| Kifurushi/Makazi | 900-BBGA,FCBGA |

| Ufungaji wa sehemu ya muuzaji | 901-FCBGA (31x31) |

| Nambari kuu ya bidhaa | XC7K420 |

FPGAs

Faida

Faida za FPGAs ni kama ifuatavyo:

(1) FPGA zinajumuisha nyenzo za maunzi kama vile seli za mantiki, RAM, vizidishi, n.k. Kwa kupanga nyenzo hizi za maunzi kimantiki, saketi za maunzi kama vile vizidishi, rejista, jenereta za anwani, n.k. zinaweza kutekelezwa.

(2) FPGA zinaweza kutengenezwa kwa kutumia michoro ya block au Verilog HDL, kutoka saketi rahisi za lango hadi saketi za FIR au FFT.

(3) FPGA zinaweza kupangwa upya kabisa, kupakia suluhu jipya la muundo katika milisekunde mia chache tu, kwa kutumia usanidi upya ili kupunguza uendeshaji wa maunzi.

(4) Masafa ya kufanya kazi ya FPGA huamuliwa na chipu ya FPGA pamoja na muundo, na inaweza kubadilishwa au kubadilishwa na chip yenye kasi zaidi ili kukidhi mahitaji fulani yanayohitajika (ingawa, bila shaka, mzunguko wa uendeshaji hauna kikomo na unaweza. iongezwe, lakini inatawaliwa na michakato ya sasa ya IC na mambo mengine).

Hasara

Hasara za FPGAs ni kama ifuatavyo:

(1) FPGA zinategemea utekelezaji wa maunzi kwa utendaji kazi wote na haziwezi kutekeleza shughuli kama vile kuruka kwa masharti kwa matawi.

(2) FPGAs zinaweza kutekeleza shughuli za uhakika pekee.

Kwa muhtasari: FPGA zinategemea maunzi kutekeleza utendakazi wote na zinaweza kulinganishwa na chip zilizojitolea kulingana na kasi, lakini kuna pengo kubwa katika unyumbufu wa muundo ikilinganishwa na vichakataji vya madhumuni ya jumla.

Kubuni lugha na majukwaa

Vifaa vya mantiki vinavyoweza kuratibiwa ni vibeba maunzi ambavyo vinajumuisha kazi zilizowekwa na maelezo ya kiufundi ya programu za kielektroniki kupitia teknolojia ya EDA.FPGA, kama mojawapo ya vifaa vya kawaida vinavyotumia njia hii, vinaelekezwa moja kwa moja na mtumiaji, vinaweza kunyumbulika sana na vinaweza kutumiwa tofauti-tofauti, ni rahisi kutumia, na ni vya haraka kufanyiwa majaribio na kutekelezwa katika maunzi.

Lugha ya Maelezo ya Vifaa (HDL) ni lugha inayotumiwa kubuni mifumo ya mantiki ya kidijitali na kuelezea saketi za kidijitali, zinazotumiwa sana ni VHDL, Verilog HDL, System Verilog na System C.

Kama lugha ya maelezo ya maunzi ya pande zote, Lugha ya Maelezo ya Maunzi ya Mzunguko ya Kasi ya Juu Sana (VHDL) ina sifa ya kutojitegemea kwa saketi mahususi ya maunzi na kutotegemea jukwaa la muundo, ikiwa na faida za uwezo wa maelezo ya masafa mapana, si. tegemezi kwa vifaa maalum, na uwezo wa kuelezea muundo wa mantiki ya udhibiti tata katika kanuni kali na mafupi, nk Inasaidiwa na makampuni mengi ya EDA na imetumiwa sana katika uwanja wa kubuni wa elektroniki.kutumika sana.

VHDL ni lugha ya hali ya juu ya muundo wa saketi, na ikilinganishwa na lugha zingine za maelezo ya maunzi, ina sifa za lugha rahisi, kunyumbulika na kujitegemea kutoka kwa muundo wa kifaa, na kuifanya kuwa lugha ya kawaida ya maelezo ya maunzi kwa teknolojia ya EDA na kufanya teknolojia ya EDA zaidi. kupatikana kwa wabunifu.

Verilog HDL ni lugha ya maelezo ya maunzi inayotumika sana ambayo inaweza kutumika katika hatua nyingi za mchakato wa uundaji maunzi, ikijumuisha uundaji wa miundo, usanisi na uigaji.

Manufaa ya HDL ya Verilog: sawa na C, rahisi kujifunza na kunyumbulika.Ni nyeti kwa kesi.Faida katika kuandika kichocheo na modeli.Hasara: makosa mengi hayawezi kugunduliwa kwa wakati wa kukusanya.

Faida za VHDL: Sintaksia kali, uongozi wazi.Hasara: muda mrefu wa kufahamiana, sio kubadilika vya kutosha.

Programu ya Quartus_II ni mazingira kamili ya muundo wa majukwaa mengi yaliyotengenezwa na Altera, ambayo yanaweza kukidhi mahitaji ya muundo wa FPGA na CPLD mbalimbali, na ni mazingira ya kina kwa muundo wa mfumo unaoweza kupangwa kwenye chip.

Vivado Design Suite, mazingira jumuishi ya muundo yaliyotolewa na muuzaji wa FPGA Xilinx mwaka wa 2012. Inajumuisha mazingira ya muundo uliounganishwa sana na kizazi kipya cha zana kutoka kwa kiwango cha mfumo hadi IC, yote yamejengwa juu ya muundo wa data wa pamoja na mazingira ya kawaida ya utatuzi.Xilinx Vivado Design Suite hutoa cores za IP za FIFO ambazo zinaweza kutumika kwa miundo kwa urahisi.